Pontificia Universidad Católica de Chile Escuela de Ingeniería Departamento de Ingeniería Eléctrica IEE2783 – Laboratorio de Sistemas Digitales

# Experiencia 2: Comunicación serial

2 Sesiones

# 1. Objetivos

Esta experiencia tiene como objetivo familiarizar al alumno con las características principales de un sistema de comunicación asíncrona y con el uso de memorias estáticas.

Lea **muy bien** esta guía antes de la sesión de laboratorio, ya que hay partes que deben ser desarrolladas previamente y serán revisadas al comienzo de la experiencia.

# 2. Instrumentos y materiales

- 1 Fuente de potencia.

- 1 Fuente generadora de funciones.

- 1 Protoboard.

- 1 EEPROM AT28C64B (8k×8).

- 1 Display de 7 segmentos doble.

- Resistores y circuitos integrados digitales varios.

### 3. Desarrollo

Antes de comenzar la experiencia procure tener todos los materiales necesarios y que su mesón de laboratorio se encuentre ordenado y libre de objetos que puedan dañar los instrumentos (principalmente líquidos).

### 3.1. Descripción general

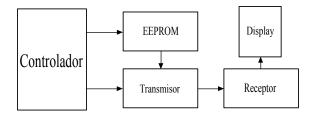

En esta experiencia cada grupo debe diseñar e implementar un sistema de comunicación serial asíncrono. El sistema considera, un controlador, un bloque transmisor (Tx), un bloque receptor (Rx) y un display. La Figura 1 muestra un diagrama de bloques del sistema a implementar.

El flujo de operación es el siguiente. El controlador debe accesar datos previamente guardados en una memoria EEPROM, los cuales son enviados al transmisor. El transmisor debe enviar mediante transmisión serial los datos al bloque receptor, el cual finalmente envía los datos recibidos a

Figura 1: Diagrama de bloques del sistema de comunicación serial asíncrona.

un display de 7 segmentos.

El formato de la señal a transmitir/recibir es el siguiente:

- En estado de reposo, Tx envía 1.

- Para iniciar la transmisión Tx envía un 0, que corresponde al *start* bit  $(B_{start})$  que sincroniza el inicio de la transmisión.

- Luego de enviar  $B_{start}$ , Tx envía el dato de siete bits, desde el bit menos significativo (LSB) al bit más significativo (MSB).

- Finalmente Tx envía un 1, que corresponde al stop bit  $(B_{stop})$  que indica el fin de la transmisión.

- Tx debe operar con un reloj interno de 2.4 kHz.

- Rx debe operar con un reloj interno de 9.6 kHz, independiente del reloj de Tx.

Además, el receptor debe verificar que el último bit recibido  $(B_{stop})$  sea efectivamente un 1. En caso de error, debe señalizarlo encendiendo un LED.

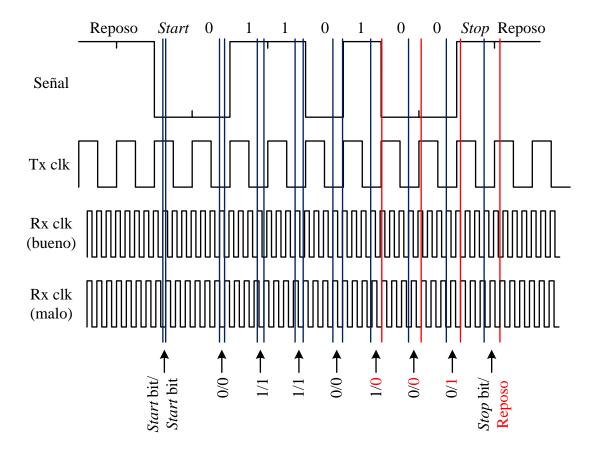

En la Figura 2 se muestra el diagrama de señales en función del tiempo para la transmisión del dato 0010110. La figura incluye la señal transmitida, el reloj de Tx y dos posibles relojes de Rx, uno bueno y otro malo. Como se puede ver, para enviar el dato primero se antepone un 0  $(B_{start})$  a la señal y se agrega un 1  $(B_{stop})$  al final de la señal. Luego de transmitir  $B_{start}$ , primero se transmite el bit menos significativo y posteriormente el resto de los bits hasta llegar al MSB, para finalmente terminar con  $B_{stop}$ . Rx, cuya señal de reloj no tiene la misma frecuencia ni tampoco está en fase con la señal de reloj de Tx, detecta  $B_{start}$ , deja pasar seis ciclos de reloj<sup>1</sup> y comienza a muestrear uniformemente cada cuatro ciclos (indicado con las líneas azules y rojas en la Figura 2).

Como fue mencionado anteriormente, en la Figura 2 se ha incluido una ilustración de un reloj de Rx demasiado lento, y por ende, malo. Puede verse que la acumulación de error hace que los bits 5, 6, 7 y  $B_{stop}$  sean muestreados fuera de posición (líneas rojas), lo que en este ejemplo en particular sólo afecta el valor real de dos de los bits transmitidos. Si la señal siguiera como se muestra en la figura, este error de ensamblaje pasaría inadvertido ya que el sistema encontraría el nivel de reposo al muestrear  $B_{stop}$ , lo que no ocurriría si Tx iniciase de inmediato la transmisión de otro dato.

<sup>&</sup>lt;sup>1</sup>En este caso particular en que la frecuencia del reloj de Rx es cuatro veces mayor que la misma de Tx, pueden ser entre 5 y 6 ciclos. Lo que se busca con esto es caer aproximadamente en la mitad del primer bit.

Figura 2: Ejemplo de comunicación serial asíncrona.

#### 3.2. Transmisor

El primer paso en la implementación del transmisor es la programación de la memoria EEPROM con la tabla de datos a transmitir. Se deben transmitir 16 caracteres de 8 bits, a elegir libremente, en un orden predefinido por cada grupo. Debe traer anotada la tabla de caracteres para facilitar la etapa de demostración del sistema. Para programar la memoria, genere el archivo binario (.bin)<sup>2</sup> con el contenido de la EEPROM. El archivo .bin que debe generar para cargar la memoria simplemente debe contener las palabras que van en la EEPROM pegadas y ordenadas (sin espacios ni saltos de líneas ni nada)<sup>3</sup>. Por ejemplo, supongamos que quiere guardar las siguientes palabras de cuatro bits en una memoria de siete palabras:

dirección 0: 0110 dirección 1: 1110 dirección 2: 0101 dirección 3: 0000 dirección 4: 1111 dirección 5: 1100 dirección 6: 0011

El archivo .bin que debe generar debería verse de la siguiente manera al abrirlo con un programa especial para ver archivos binarios, no cualquier editor de texto:

#### 01101110010100001111111000011

Sea sumamente cuidadoso al manipular la memoria<sup>4</sup>.

El funcionamiento del bloque transmisor debe cumplir con las siguientes especificaciones:

- 1. La comunicación de la tabla de caracteres debe comenzar con una señal generada a mano.

- 2. Entre caracter y caracter el transmisor debe hacer una pausa de 1 segundo y debe detenerse cuando se haya completado la transmisión de los 16 caracteres. Una vez finalizada la transmisión, el transmisor debe estar listo para retransmitir en cualquier momento.

Para implementar el transmisor puede usar simplemente *shift registers* con carga paralela y un *push-button* para iniciar la transmisión. **Debe presentar su diseño del transmisor al comienzo** de la primera sesión de esta experiencia. En el caso contrario, podrá optar a un máximo de 5 en la nota final de la experiencia.

## 3.3. Receptor

Para implementar el receptor puede usar *shift registers* con carga serial y salida paralela. La señal de reloj usada para la recepción debe ser **totalmente independiente** de la señal de reloj usada para la transmisión. Recuerde que debe mostrar los datos transmitidos en un display de 7 segmentos doble, por lo que se recomienda investigar sobre las conexiones necesarias. En el laboratorio encontrará displays de 2 tipos: ánodo común y cátodo común.

<sup>&</sup>lt;sup>2</sup>Puede usar Matlab para generar su archivo .bin

<sup>&</sup>lt;sup>3</sup>Puede descargar un programa para ver archivos binarios.

<sup>&</sup>lt;sup>4</sup>Para cargar su archivo en la memoria consulte al profesor o a sus ayudantes. El laboratorio cuenta con un programador. De todas maneras, familiarícese por su cuenta con el programador de EEPROM MaxLoader

# 4. Informe

En su informe de experiencia debe incluir lo siguiente:

- 1. Diseño conceptual de su sistema (explique en palabras como entiende el funcionamiento y visualiza la solución).

- 2. Diagrama de bloques de su solución.

- 3. Diseño completo del transmisor y receptor.

- 4. Discusión y conclusiones (comente sobre su impresión de la experiencia y proponga mejoras).

## 5. Evaluación

Una vez finalizada la experiencia cada grupo debe realizar una demostración de su circuito y contestar preguntas sobre su diseño e implementación.

La nota de la experiencia se distribuye como:

- Funcionamiento del circuito: 60 %.

- Informe: 30 %.

- Preguntas hechas durante la demostración: 10 %.